Bildbasiertes Oberflächenscreening sorgt für präzise Fehlererkennung

In der Produktion von hochpräzisen Mikroelektronikchips ist eine genaue Überprüfung der Qualität essenziell. In der Halbleiterfertigung kommen allerdings klassische automatisierte Bilderkennungssysteme schnell an ihre Grenzen. Daher nützt Infineon Künstliche Intelligenz (KI), um tausende Bilder von Chipoberflächen zeitgerecht auf Auffälligkeiten zu inspizieren. Fraunhofer Austria, insbesondere das Innovationszentrum KI4LIFE in Klagenfurt, unterstützte die Infineon Technologies Austria AG und die KAI Kompetenzzentrum Automobil- und Industrieelektronik GmbH im Rahmen des Projekts ImageCop bei der Entwicklung des dafür nötigen neuronalen Netzes und brachte Erkenntnisse zur Anwendung, die in der Grundlagenforschung gerade erst gewonnen worden waren.

Die Infineon-Halbleiterlösungen begegnen uns täglich in vielen Anwendungen: Ob im Zug, im Auto, in E-Ladestationen, erneuerbarer Energien oder im Industrieroboter. Mikrochips von Infineon verbessern die Energieeffizienz und die Sicherheit. In Zügen ermöglichen Module von Infineon energieeffiziente Antriebe. Sensoren, Mikrocontroller und Sicherheitslösungen in Autos und in der E-Mobilität zielen darauf ab, energieeffizientes und automatisiertes Fahren Wirklichkeit werden zu lassen und schon heute unterstützen Radarsysteme die Sicherheit beim Fahren, indem sie beispielsweise Objekte oder Personen auf der Straße zuverlässig erkennen. Damit all diese Systeme perfekt funktionieren, sind Tests und eine strenge Qualitätskontrolle ein Pflichtbestandteil in der Chipproduktion.

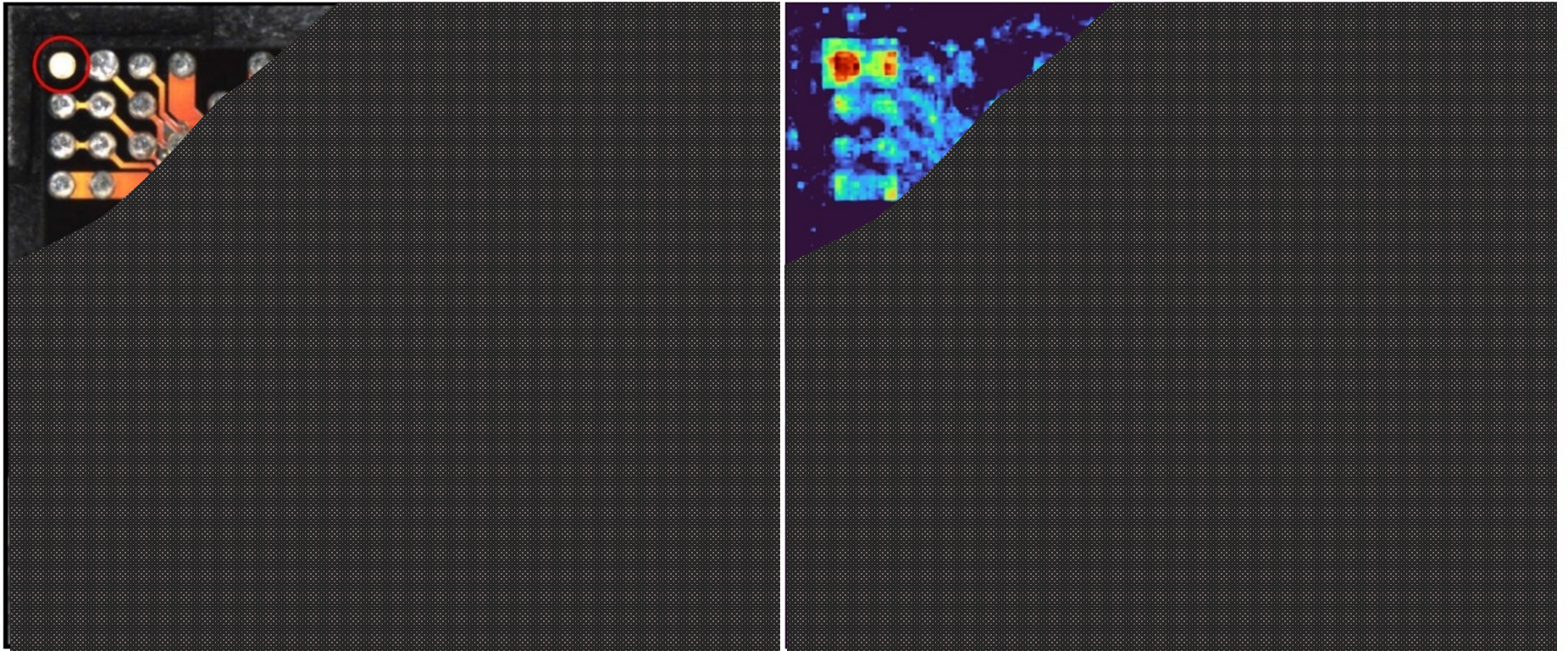

Im Rahmen dieser Kontrollen werden die Bauteile fotografiert. Tritt ein Fehler auf, werden diese Bilder verwendet, um die Fehlerursache feststellen zu können. Nun ist es aber das Ziel, sämtliche Chips und Bilder vollautomatisch zu überprüfen. Eine Herausforderung ergab sich bezüglich der KI-Methode: durch die hohe Qualität der Produktion sind bislang schon kaum fehlerhafte Chips zu finden, anhand derer man eine KI hätte trainieren können.

Seltene Fehler

„Will man eine KI entwickeln, die Fehler erkennt, dann muss man dem System beibringen, was ein Fehler ist und was nicht. Im Supervised Deep Learning braucht man dafür normalerweise sehr, sehr viele Bilder, und zwar nicht nur von guten Beispielen, sondern vor allem auch von möglichen Fehlern“, erklärt Ulrich Krispel, der bei Fraunhofer Austria die Projektleitung für ImageCop innehat. Da die Fehler in der Halbleiterproduktion von Infineon aber äußerst selten sind, musste das Team eine andere Herangehensweise wählen. „Mangels einer statistisch repräsentativen Anzahl fehlerhafter Chips haben wir, anstatt die Fehler zu definieren, aus den bekannten Daten der zahlreichen guten Beispiele das KI Verfahren ein Modell der Normalität, also ein Modell eines einwandfreien Chips, lernen lassen. Ein Fehler wird dann als Abweichung von diesem Normalmodell erkannt. Dabei handelt es sich um Anomalieerkennung, ein statistisches Verfahren“, erklärt Ulrich Krispel.

Die Forscher griffen dabei auf jüngste Erkenntnisse aus der Grundlagenforschung zurück: Beim Einsatz des sogenannten „Transfer Learning“ wird ein vortrainiertes neuronales Netz verwendet, um relevante Bildinformation („Features“) aus den Beispielbildern zu extrahieren. Mit diesen Features wird das Normalmodell aus den Beispielbildern erzeugt. Durch die Verwendung des vortrainierten Netzes muss man kein aufwendiges Training durchführen und benötigt dabei auch weniger Beispielbilder. Im letzten Jahr wurden mehrere Verfahren publiziert, in denen ein solches bildbasiertes Normalmodell die örtliche Erkennung von Anomalien ermöglicht.

Nun haben die Forscherinnen und Forscher des ImageCop Projekts die nötigen Anpassungen und Weiterentwicklungen vorgenommen, um ein solches Verfahren auf reale Bilder aus der Chipindustrie anwenden zu können. Bereits im Lauf des Jahres 2022 soll das System implementiert werden.

Große Varianz

Als besondere Herausforderung erwies sich bei der Entwicklung des Verfahrens die große Varianz im Aussehen der funktionierenden Chips. „Die Testumgebung ist kein Reinraum. Daher befinden sich auch optisch erkennbare Objekte wie zum Beispiel kleine Staubpartikel oder ähnliches auf der Oberfläche. Diese werden aber nicht als Fehler dargestellt. Zudem werden Chips für das Testverfahren gestresst, das heißt, sie werden elektrischen Belastungen und Temperaturschwankungen ausgesetzt, um den Betrieb unter realen Bedingungen zu simulieren. Das alles führt zu Spuren an der Oberfläche der Chips, die aber kein Anzeichen für etwaige Fehler sind und daher vom System als normal eingestuft werden sollen“, erklärt Ulrich Krispel. Eine klassische Bildanalyse würde hinsichtlich der großen Varianz also nicht zum Ziel führen, wohl aber das gelernte Modell eines normalen Chips, das das Forschungsteam im Rahmen des Projekts erstellt hat. Dieses kann auch erfolgreich mit Helligkeits- und Farbänderungen bei unterschiedlichen Bauteilen gleicher Bauart umgehen.

„Die drei Forschungspartner Infineon, KAI und Fraunhofer Austria haben in diesem Projekt ein starkes Dreieck gebildet, das in kürzester Zeit einen beeindruckenden Algorithmus entwickelt hat. Die Kompetenzen aller Beteiligten haben sich ideal ergänzt und zu einem hervorragenden Projektergebnis geführt“, sagt Eva Eggeling, Leiterin des Fraunhofer Austria Innovationszentrums KI4LIFE.

Der vorliegende Beitrag wurde teilweise durch das europäische Forschungsvorhaben iRel40 finanziert, das vom ECSEL Joint Undertaking (JU) unter der Fördervereinbarung Nr. 876659 gefördert wird. Das JU erhält Unterstützung aus dem Forschungs- und Innovationsprogramm Horizon 2020 der Europäischen Union, sowie von Deutschland, Österreich (BMVIT-IKT der Zukunft, FFG-Projekt Nr. 877540), Slowakei, Schweden, Finnland, Belgien, Italien, Spanien, Niederlande, Slowenien, Griechenland, Frankreich, Türkei. Die in dieser Veröffentlichung enthaltenen Informationen und Ergebnisse sind die der Autoren und spiegeln nicht zwingend die Meinung des ECSEL Joint Undertaking wider.

Fraunhofer Austria

Fraunhofer Austria